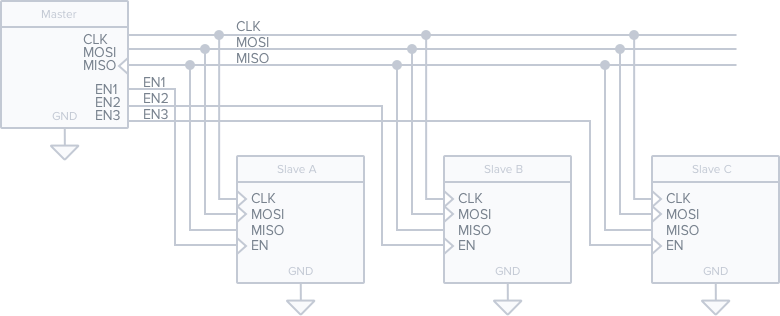

SPI Signals & Topology

- CLK (Clock)

- MOSI (Master Out, Slave In; Most-Significant bit first)

- MISO (Master In, Slave Out; Most-Significant bit first)

- SS (Slave Select, active low; aka Enable/EN)

SPI has two mode bits, CPOL (Clock Polarity), and CPHA (Clock Phase).

CPOL = 0, CPHA = 0

- CLK starts out LOW

- MOSI/MISO is read on each RISING edge of CLK.

CPOL = 0, CPHA = 1

- CLK starts out LOW

- MOSI/MISO is read on each FALLING edge of CLK.

CPOL = 1, CPHA = 0

- CLK starts out HIGH

- MOSI/MISO is read on each FALLING edge of CLK.

CPOL = 1, CPHA = 1

- CLK starts out HIGH

- MOSI/MISO is read on each RISING edge of CLK.

Debugging SPI

The best tool to use to debug and verify SPI is the Saleae Logic.

(full disclosure, we make this product - but ask your embedded developer friends and we think you'll get the same answer.)

The Saleae Logic can decode SPI, I2C, serial, 1-Wire, CAN, and 19+ more common digital protocols. Here's a short video showing decoding of I2C.

Is this SPI Quick Reference missing any crucial details? Please let us know - support@saleae.com.